Fabrication of silicon photonics with integrated III–V materials at scale

Advances in computing power continue to move at a faster pace than those for interconnects, and this creates a bottleneck within artificial intelligence (AI)-scale data centers. Unless interconnects can improve, this is likely to become the limiting factor in enabling next-gen architectures needed to support complex large language and inference models.

To minimize this bottleneck and meet the needs of the exponentially growing amount of data center traffic, the industry needs to deliver optical interconnects not only with increased bandwidth and increased energy efficiency but it must evolve to be able to deliver it at scale.

Silicon photonics

Silicon photonics and its ability to be manufactured using complementary metal-oxide semiconductor (CMOS) processes has naturally emerged as a dominant technology to meet the needs of the hyperscalers. But standard silicon photonics comes with several intrinsic limitations.

Notably, silicon as a material is unable to generate light, so existing solutions require the use of external lasers coupled via micro-optics. It significantly increases the physical footprint, cost, and packaging complexity—even with advanced techniques, it’s an inherently lossy process. And even with the brightest and most efficient lasers, which are made of indium phosphide (InP), this is by far the largest contribution to the power consumption of interconnect optics.

Silicon modulators are also struggling to support data rates above the industry standard of 200G per lane having an intrinsic bandwidth of around 50 GHz. This limitation comes from the properties of silicon. Modulators fabricated in InP have been proven to have a bandwidth in excess of 100 GHz, which enables a modulation speed of 400G per lane.

III-V materials

The use of heterogeneous integration of III-V materials, particularly InP, directly onto silicon wafers offers a solution to both limitations of silicon photonics. This approach enables the production of fully integrated photonic integrated circuits (PICs) that feature on-chip lasers, optical amplifiers, and compact electro-absorption modulators (EAMs) on a silicon-based platform, which can be implemented within standard CMOS foundries. And it allows these higher-density, lower-power photonic components to still be manufactured at scale.

Packaging and alignment

A primary challenge to scaling photonic integration is that traditional methods tend to rely on complex packaging to couple external light sources to the silicon chip, and/or require precise mechanical alignment during the bonding of active elements.

Conversely, by bonding III-V epitaxial die (chiplets) to patterned silicon wafers and processing within the foundry, it is possible to eliminate the need for high-precision alignment. Instead, this alignment with the underlying silicon passive components can be undertaken during the lithography phase, with processing of the diodes and definition of the active components taking place after the bonding is complete.

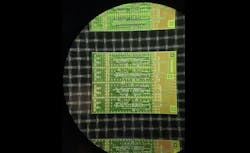

This approach not only enables a tighter integration with lower losses between the active elements and the waveguides, but also a higher yield vs. techniques that require high mechanical placement accuracy. It creates a wafer that resembles a standard silicon photonics wafer that can be handled, tested, and post-processed like any other silicon wafer, but possesses regions of III-V material capable of light generation, amplification, and high-speed modulation.

From a form factor perspective, silicon modulators are typically Mach-Zehnder modulators (MZMs) and will occupy several square millimeters of valuable chip space. A heterogeneous platform’s InP-based electro-absorption modulators (EAMs) have a footprint of just a few hundred square microns.

Performance comparisons

Shifting from theory to the real world, OpenLight’s 200G per lane InP EAM devices are already production-ready, with 400G per lane component samples recently received back and testing started.

Looking first to the 200G per lane devices, independent testing (in collaboration with Riga Technical University and Keysight) shows the current design is able to deliver a 3-dB bandwidth of approximately 60 GHz. In testing, the devices enabled successful 224 Gbit/s PAM4 transmission over distances of 6 km while remaining below forward error correction (FEC) limits.

Transitioning from 200G to 400G does not, however, require a total redesign of the modulator’s active region. Instead, our engineering team was able to evolve the existing 200G design by optimizing the active region and redesigning the electrical interface to accommodate higher bandwidths, including supporting differential drive that’s expected to be needed at this bit rate. Current work within the lab now involves further improving the bandwidth incrementally and ensuring other parameters of the modulator are not impacted while improving the yield and manufacturability.

Energy efficiency and reliability

Testing of the integrated distributed feedback (DFB) lasers showed a power of 30 mW per facet, and a wall plug efficiency (WPE) of 15% at nominal operating temperatures of 40°C (>11% at 80°C). While this may seem a modest power, it is more than sufficient to design a transceiver PIC that meets the IEEE standard for optical modulation amplitude (OMA) with either parallel single-mode or coarse wavelength division multiplexing (CWDM) configurations. This is accomplished due to the low coupling loss between the active devices and the waveguides of both the laser and the modulator, coupled with the low loss that silicon waveguides provide.

In terms of reliability, we performed qualification tests based on the GR-468 standard. Laser structures show that zero failures were observed after 5,000 hours of high-temperature operating life (HTOL) tests across three independent lots, and long-term evaluation of a specific lot has now exceeded 10,000 hours of continuous operation without failure or performance degradation.

Integration into a transceiver architecture

The true potential of the III-V-on-silicon platform can be best seen if we look at the density and manufacturability possible from a single, monolithic PIC. As highlighted, additional componentry required for traditional pluggable optics creates sprawling layouts that take up valuable real estate.

When factoring in four integrated DFB lasers to drive eight high-speed EAM modulators and even incorporating booster semiconductor optical amplifiers at the output to give improved link budgets, the entire architecture for either a 1.6T or 3.2T device can be achieved within a 5 × 7-mm area. Because these functions are integrated by the incorporation of III-V devices within the PIC, this is an entire self-contained transmitter that can be fabricated and tested as a single unit at wafer scale. Assembly into a variety of form factors, including pluggable, near, or copackaged optics, is much closer to the well-established electronics flow to enable high-throughput and cost-effective manufacturing.

More on OpenLight

About the Author

Molly Piels

Molly Piels, Ph.D., is a principal engineer and PIC design expert for OpenLight (Goleta, CA).