Advanced semiconductor packaging meets photonics: Copackaged optics for data centers

Driven by the demands of artificial intelligence (AI) and high-performance computing (HPC), a critical convergence is taking place across three critical domains: Advanced semiconductor packaging, photonics, and networking. Central to this transformation is copackaged optics (CPO), which integrate optical and electronic functions within the same package to enable faster, more energy-efficient data transfer between processing units and network devices.

Limitations of traditional architectures

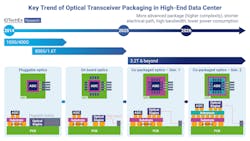

During the past decade, data center switch capacity has grown rapidly—from 0.64 Tbps to more than 25.6 Tbps, driven by the adoption of 64x 400 Gbps or 32x 800 Gbps pluggable optical transceiver modules. But these pluggable optics, which reside on the edge of the printed circuit board (PCB), are nearing their limits in terms of power consumption, signal integrity, and form factor constraints. To support next-generation optical engines at 800 Gbps and beyond, lane rates must reach at least 100 Gbps, which intensifies signal integrity issues across the switch socket, motherboard, and connectors, and drives up serializer/deserializer (SerDes) power consumption. In future Ethernet switching, input/output (I/O) power could surpass core power, while the density limits of QSFP/OSFP modules and the need for advanced thermal solutions pose additional challenges.

This has led to an important industry shift: Bringing optical engines closer to the switch application-specific integrated circuits (ASICs) to reduce copper interconnect lengths. While front-panel pluggables remain dominant today, they are unlikely to scale to 1.6T and 3.2T systems without substantial efficiency losses. CPO is the solution to this issue.

CPO: Intersection of optics, packaging, and networking

CPO places the optical transceiver next to or atop the switch or compute die within a single package. This significantly reduces the electrical channel length, minimizes signal degradation, cuts SerDes power, and increases bandwidth density.

In recent implementations, power savings of 30 to 50% were reported compared to traditional pluggable modules. By shortening the copper path, designers can either operate at lower SerDes speeds or entirely bypass the need for high-speed copper drivers, which enables more scalable architectures for AI-centric data centers.

The implications are profound for networking. In systems like NVIDIA’s DGX NVL72 AI server, which uses more than 5,000 copper wires to interconnect compute nodes via NVLink switches, the signal integrity burden is enormous. Retimers are needed, latency increases, and thermal budgets become strained. IDTechEx projects that next-generation architectures will eliminate such switches entirely by replacing copper backplane networks with direct optical connections between compute nodes; it will be facilitated by CPO.

Role of advanced semiconductor packaging

Advanced semiconductor packaging plays a central role enabling CPO by allowing the optical engine (OE)—which comprises photonic integrated circuits (PICs) and electronic integrated circuits (EICs)—to be integrated alongside switch ASICs or extended processing units (XPUs) on a single package substrate. Packaging strategies for CPO typically fall into two categories: One focuses on the standalone packaging of the optical engine, and the other on its cointegration at the system level with high-performance ICs such as ASICs or XPUs. Both require the deployment of advanced 2.5D and 3D semiconductor packaging technologies to achieve the necessary density, bandwidth, and power efficiency. IDTechEx's latest report, “Co-Packaged Optics 2025-2035: Technologies, Market, and Forecasts,” delves into how various packaging technologies facilitate the heterogeneous integration of CPO.

CPO relies on techniques such as:

2.5D integration, where PICs and EICs are mounted on an interposer with through-silicon vias (TSVs). In comparison to conventional 2D integration, this setup reduces parasitics via microbumps or copper pillars, which enables higher I/O density and improved bandwidth. Interposers can also incorporate waveguide layers to enhance optical signal routing. While more advanced than 2D, 2.5D integration incurs higher costs and still has greater parasitics than 3D integration, which limits its performance in some high-end applications.

3D hybrid bonding, which takes a more advanced approach by vertically stacking the EIC atop the PIC using technologies like TSVs, high-density fanout, copper-copper (Cu-Cu) hybrid bonding, or photonic interposers. This method significantly reduces parasitics, supports fine-pitch interconnects, and improves performance. But it introduces thermal challenges due to heat generated by the EIC affecting the underlying PIC, requiring advanced cooling solutions. Cu-Cu hybrid bonding holds potential to enable ultradense, low-loss interconnects essential for next-generation CPO designs. TSMC is at the forefront of this development through its 3D system-on-integrated-chips (SoIC-X) technology and compact universal photonic engine (COUPE) platforms, because it enabled the world's first 3D-stacked silicon photonic engines in collaboration with NVIDIA. These innovations are exemplified within NVIDIA’s Spectrum-X and Quantum-X platforms, which deliver up to 400-Tbps bandwidth in compact, thermally efficient CPO-based network switches.

While these integration approaches offer major benefits, they also introduce new challenges. For example, precise optical alignment, low-loss waveguide integration, and effective thermal management of densely packed optical and electronic components are all critical challenges that need to be addressed. Manufacturing complexity, material compatibility issues, and the need for new testing methods further complicate scaling. Balancing electrical, optical, and thermal requirements is critical for reliable high-volume deployment.

CPO: A growing $1.2B market opportunity

CPO is rapidly progressing from concept to demonstration and approaching commercialization. Companies like Nvidia, Cisco, Broadcom, Intel, and Ranovus are showcasing advanced prototypes, with Nvidia set to launch CPO-based network switch platforms by 2026. A collaborative ecosystem is emerging across foundries, outsourced semiconductor assembly and test (OSAT) companies, fiber module suppliers, and AI infrastructure providers.

IDTechEx projects the CPO market will exceed $1.2B by 2035, growing at a CAGR of 28.9% from 2025 to 2035. CPO-enabled switches will account for the majority of this revenue, but optical interconnects for AI accelerators will represent nearly 20% of the market. With optical I/O adoption expected to scale rapidly across hyperscalers and compute vendors, CPO stands as a cornerstone for the future of scalable, energy-efficient, and high-performance infrastructure.

About the Author

Yu-Han Chang

Yu-Han Chang is a principal technology analyst at IDTechEx (Cambridge, U.K.), which provides trusted independent research on emerging technologies and their markets.