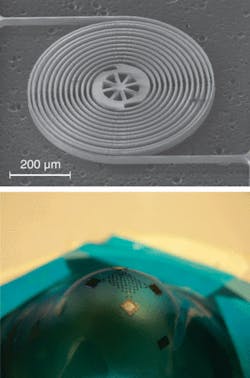

The expandable silicon is fabricated by using deep reactive-ion etching to create 30-µm-thick (although thicknesses up to 100 µm have been demonstrated), 200-µm-diameter circular silicon islands surrounded by 1.6-µm-thin spiral ribbons of silicon that act as springs. Each island can be a custom integrated circuit with unique electronics and electrical interconnects that run along the top of the coiled silicon wires to provide connectivity to other islands.

To uncoil the spiral ribbons, the devices are transferred to an electrostatic chuck, where stainless-steel probes manipulate pads at the corner of the coiled structures to expand the devices into an array. Once the desired size is achieved, the array is transferred to an adhesive surface. Although as many as 71 islands have been stretched to an array with an area 50 times larger than the uncoiled area of the structures, longer spiral springs could further extend this “expandable” network.

Surprisingly, the structures are quite robust; the coils can be fully extended multiple times without breaking and no delamination of the silicon dioxide coating used to overlay the final structures has been observed.

One unique product being explored by the research team is a curved focal-plane array that, by nature of its shape, eliminates many of the off-axis color mixing and image noise problems inherent in flat arrays. The curved array not only conforms to any shape (reducing the cost of imaging optics), but also offers single-crystal silicon performance in a low-cost, distributed configuration.

In early 2007, Stanford University researcher Peter Peumans founded NetCrystal (Mountain View, CA) to make solar panels using the expandable silicon arrays. He expects to make microconcentrator silicon solar arrays that are three times cheaper than comparable silicon solar panels. “The cost reductions come chiefly from a reduction in the cost of silicon and processing,” says Peumans. “The modules can be made flexible and can be readily integrated into building materials.”

“This is a platform technology that allows you to use monolithic silicon in entirely new applications such as smart materials,” says Kevin Huang, a Ph.D candidate working with Peumans. “Basically, it enables large-area electronics to benefit from the high performance and rapidly decreasing cost per function of CMOS technology.”

REFERENCE

1. K. Huang et al., IEDM 2007 Conf., Washington, D.C., session 9, paper 9.2 (December 2007).